Home /

Expert Answers /

Computer Science /

use-vhdl-design-a-mod-12-counter-using-the-4-bit-binary-counter-designed-above-designing-mod-pa130

(Solved): Use VHDL Design a mod-12 counter using the 4-bit binary counter designed above. Designing mod ...

Use VHDL

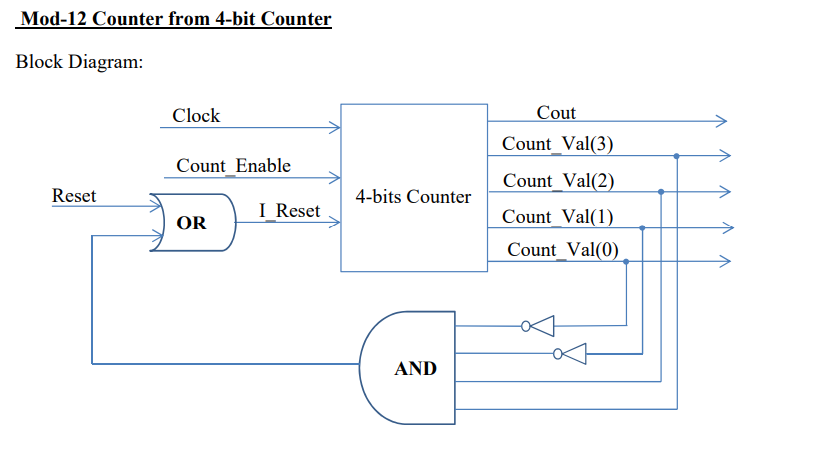

Design a mod-12 counter using the 4-bit binary counter designed above. Designing “mod” counters involves “clearing” the counter at the specified count. It may involve adding a new NAND gate entity to clears the circuit.

Include:

? VHDL program

? VHDL test bench with enough test cases

? Waveform with comments

Note: mod-12 counter means that the counter will automatically reset to 0 after counting to 11

For example: 0 1 2 3 4 5 6 7 8 9 10 11 0 1 2 3 4 5 6 7 8 9 10 11 0 1 2 . . . . . . . .

Mod-12 Counter from 4-bit Counter Block Diagram:

Expert Answer

Loads the waveform into VHDL (Note: You need a VHDL waveform library). below 1. The counter is based on 4-bit binary counters. As explained earlier, the counter works by applying 32 logic functions to each bit of data, so initially it has 2^4=16=32