Home /

Expert Answers /

Electrical Engineering /

use-the-data-flow-modeling-case-statement-to-simulate-the-verilog-code-for-the-4-to-1-multiplexe-pa415

(Solved): Use the Data Flow modeling (case statement) to simulate the Verilog code for the 4-to-1 multiplexe ...

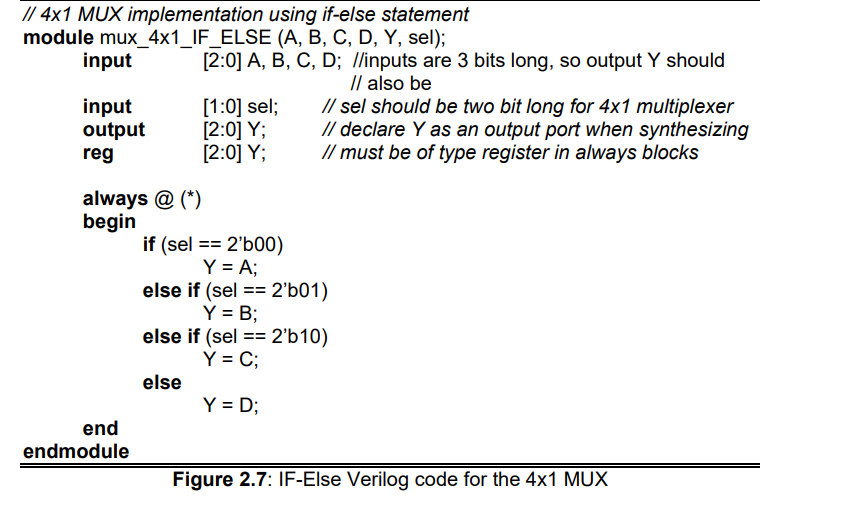

Use the Data Flow modeling (case statement) to simulate the Verilog code for the 4-to-1 multiplexer circuit, see Figure 2.7 as reference.

// 4x1 MUX implementation using if-else statement module mux_4x1_IF_ELSE (A, B, C, D, Y, sel); input input output reg always @ (*) begin end endmodule [2:0] A, B, C, D; //inputs are 3 bits long, so output Y should // also be [1:0] sel; [2:0] Y; // sel should be two bit long for 4x1 multiplexer // declare Y as an output port when synthesizing // must be of type register in always blocks [2:0] Y; if (sel == 2'b00) Y = A; else if (sel == 2'b01) Y = B; else if (sel == 2'b10) Y = C; else Y =D; Figure 2.7: IF-Else Verilog code for the 4x1 MUX

Expert Answer

//4x1 MUX using case statement module mux_4x1_case_statement(A,B