Home /

Expert Answers /

Electrical Engineering /

exercise-3-design-a-3-bit-by-2-bit-binary-multiplier-1-derive-the-function-for-the-full-adder-st-pa135

(Solved): Exercise 3: Design a 3-bit by 2-bit binary multiplier 1. Derive the function for the full adder st ...

Exercise 3: Design a 3-bit by 2-bit binary multiplier 1. Derive the function for the full adder studied in the previous lab. 2. Derive a closed form formulation to the multiplication of a 3-bit input \( \left[A_{2}, A_{1}, A_{0}\right] \) by a 2-bit input \( \left[B_{1}, B_{0}\right] \). The output would be \( \left[M_{4}, M_{3}, M_{2}, M_{1}, M_{0}\right] \) 3. Build the corresponding circuit. Please note, in Logisim, they used a not very common definition for the XOR gates with 3 or more inputs instead of the industry common standard of using it as a parity (equals to cascading two XOR gates, each with 2 inputs). Therefore, in Logisim, use only XOR gates with two inputs. Do not use XOR gates with more than 2 inputs in Logisim. 4. Enable logging of the inputs ( \( A \) and \( B \) ) and output \( M \) to a file name 'Lab3_Ex3_log.txt', while using radix \( -10 \) 5. Simulate the circuit by using the poke tool, to test all the possible inputs. 6. Save the circuit as 'Ex3.circ'. Congratulations. Now you can design a fully functioning MUL instruction with arbitrary size inputs/outputs.

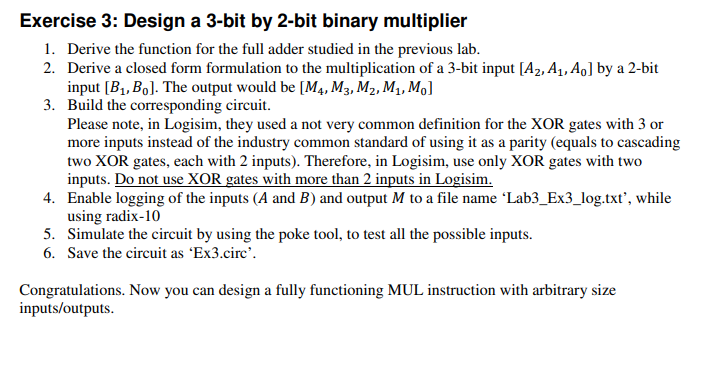

Derive a closed form formulation to the multiplication of a 3 -bit input \( \left[A_{2}, A_{1}, A_{0}\right] \) by a 2-bit input \( \left[B_{1}, B_{0}\right] \). The output would be \( \left[M_{4}, M_{3}, M_{2}, M_{1}, M_{0}\right] \) :

![Derive a closed form formulation to the multiplication of a 3 -bit input \( \left[A_{2}, A_{1}, A_{0}\right] \) by a 2-bit in](https://media.cheggcdn.com/media/08a/08a56809-fbee-4183-aacc-304846d58d9d/php5hYZH4)