Home /

Expert Answers /

Electrical Engineering /

4-20-pts-we-have-a-risc-v-pipeline-design-shown-below-we-are-trying-to-support-a-new-instructio-pa684

(Solved): 4. (20 pts) We have a RISC-V pipeline design shown below. We are trying to support a new instructio ...

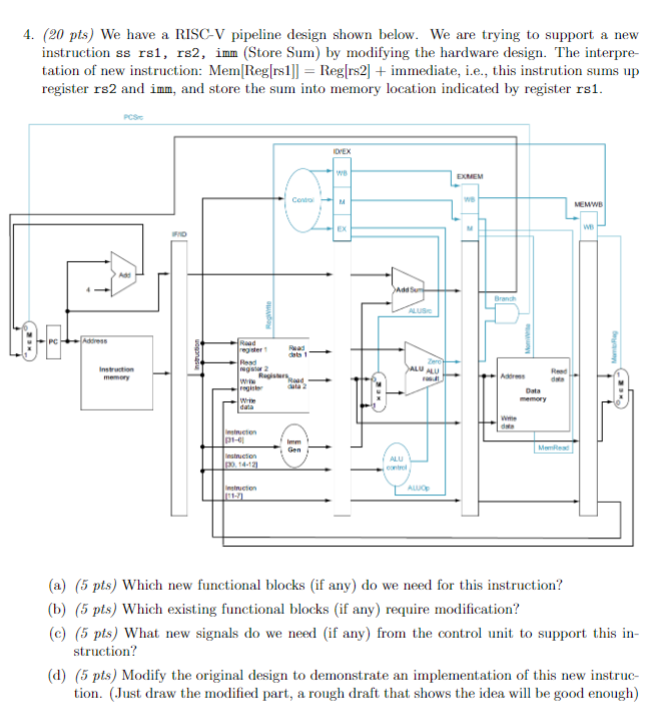

4. (20 pts) We have a RISC-V pipeline design shown below. We are trying to support a new instruction ss rs1, rs2, imm (Store Sum) by modifying the hardware design. The interpretation of new instruction: Mem[Reg[rs1]] = Reg[rs2] + immediate, i.e., this instrution sums up register and imm, and store the sum into memory location indicated by register rs1. (a) ( 5 pts) Which new functional blocks (if any) do we need for this instruction? (b) (5 pts) Which existing functional blocks (if any) require modification? (c) (5 pts) What new signals do we need (if any) from the control unit to support this instruction? (d) ( 5 pts) Modify the original design to demonstrate an implementation of this new instruction. (Just draw the modified part, a rough draft that shows the idea will be good enough)

Expert Answer

RISC-V (Reduced Instruction Set Computer-V) architecture is an open-source instruction set architecture (ISA) that is gaining popularity in the industry and academia. One important aspect of any processor architecture, including RISC-V, is its pipeline design, which plays a crucial role in achieving high performance and efficiency.The RISC-V pipeline is designed to execute instructions in a sequential and overlapping manner, utilizing multiple stages to perform different tasks on each instruction. a)