Home /

Expert Answers /

Electrical Engineering /

3-in-the-finite-state-machine-below-the-d-flip-flop-outputs-serve-as-output-of-the-system-a-obt-pa679

(Solved): 3. In the finite state machine below the D-flip-flop outputs serve as output of the system. a) Obt ...

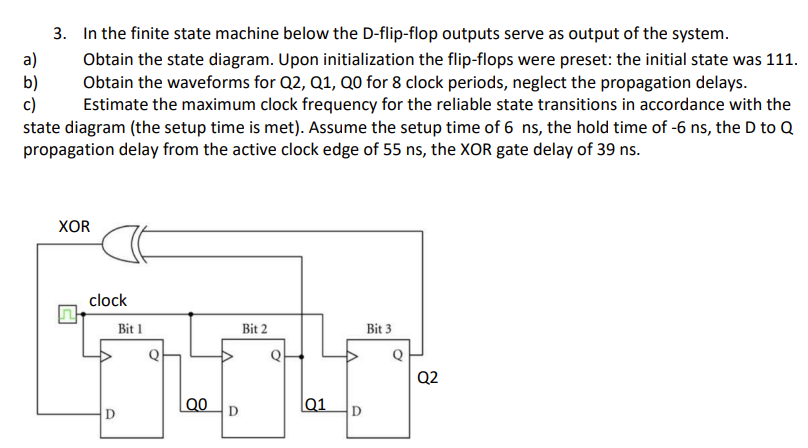

3. In the finite state machine below the D-flip-flop outputs serve as output of the system. a) Obtain the state diagram. Upon initialization the flip-flops were preset: the initial state was 111. b) Obtain the waveforms for Q2, Q1, Q0 for 8 clock periods, neglect the propagation delays. c) Estimate the maximum clock frequency for the reliable state transitions in accordance with the state diagram (the setup time is met). Assume the setup time of 6 ns, the hold time of -6 ns, the D to Q propagation delay from the active clock edge of 55 ns, the XOR gate delay of 39 ns.

3. In the finite state machine below the D-flip-flop outputs serve as output of the system. a) Obtain the state diagram. Upon initialization the flip-flops were preset: the initial state was 111. b) Obtain the waveforms for Q2, Q1, Q0 for 8 clock periods, neglect the propagation delays. c) Estimate the maximum clock frequency for the reliable state transitions in accordance with the state diagram (the setup time is met). Assume the setup time of \( 6 \mathrm{~ns} \), the hold time of \( -6 \mathrm{~ns} \), the \( D \) to \( Q \) propagation delay from the active clock edge of \( 55 \mathrm{~ns} \), the XOR gate delay of \( 39 \mathrm{~ns} \).