Home /

Expert Answers /

Electrical Engineering /

3-bit-0-bit-3-bit-2-bit-1-bit-4-what-are-the-required-bits-and-what-do-they-need-to-be-in-order-for-pa793

(Solved): 3. bit 0 bit 3 bit 2 bit 1 bit 4 What are the required bits and what do they need to be in order for ...

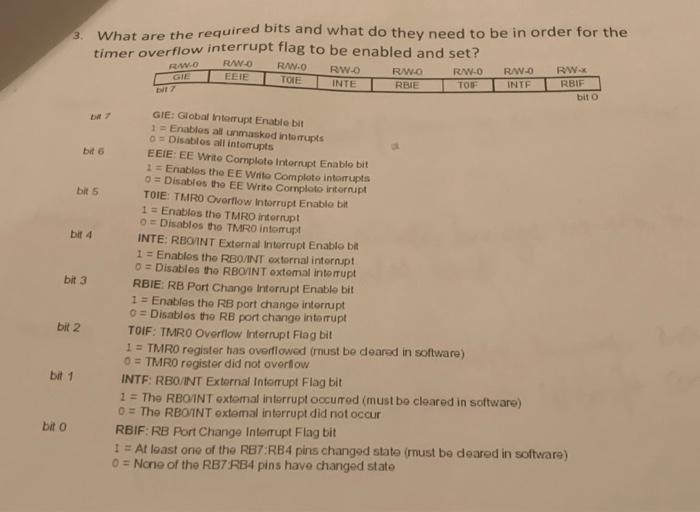

3. bit 0 bit 3 bit 2 bit 1 bit 4 What are the required bits and what do they need to be in order for the timer overflow interrupt flag to be enabled and set? R/W-0 R/W-0 TOIE EEIE bit 7 bit 6 bit 5 R/WWW-0 GIE bit 7 GIE: Global Interrupt Enable bit 1 = Enables all unmasked interrupts 0 = Disables all interrupts RW-0 INTE EEIE: EE Write Complete Interrupt Enable bit 1 = Enables the EE Write Complete interrupts 0 = Disables the EE Write Complete interrupt TOIE: TMRO Overflow Interrupt Enable bit 1 = Enables the TMRO interrupt 0 = Disables the TMRO interrupt INTE: RBO/INT External Interrupt Enable bit 1= Enables the RBO/INT external interrupt 0 = Disables the RBOVINT extemal interrupt RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt R/W-O RBIE R/W-0 TOIF TOIF: TMRO Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be deared in software) 0= TMR0 register did not overflow R/WW-0 INTE INTF: RBO/INT External Interrupt Flag bit 1 = The RBO/INT extemal interrupt occurred (must be cleared in software) 0 = The RBO/INT extemal interrupt did not occur RW-X RBIF bit O RBIF: RB Port Change Interrupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) 0 = None of the RB7:RB4 pins have changed state

3. What are the required bits and what do they need to be in order for the timer overflow interrupt flag to be enabled and set? bit 7 GIE: Global interrupt Enable bil 1 = Enablos all unmasked intorupts Disables all intomupts EEIE: EE Write Comploto Interrupt Enable bit Erables the EE Whito Comploto interrupts Disabies the EE Write Comploto interupt bit 5 TOIE: TMR0 Overllow interrupt Enable bit Enablos tho TMRO intorrupt Disables tho TMRO intorupt bit 4 INTE: REOINT External interrupt Enable bit Enablos the RBOAINT external intornpt Disables the RBOINT extemal intorupt bit 3 RBIE: RB Port Change Intorupt Enablo bit Enables the RB port change internupt Disables the RB port change interupt bit 2 TOIF: TMR0 Overtlow Interrupt Flag bit 1 = TMRO register has overtlowod (must be deared in software) TMRO register did not overfiow. INTF: RBO/NT External Interrupt Flag bit The RBOINT extemal interrupt oocured (must be cleared in software) The RBOTNT extemal interrupt did not occur RBIF: RB Fort Change intertupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be deared in software) None of the RB7 RB4 pins have changed state