(Solved): 11.5 The binary number 11100011 is serially right-shifted into an 8 -bit SIPO shift register with an ...

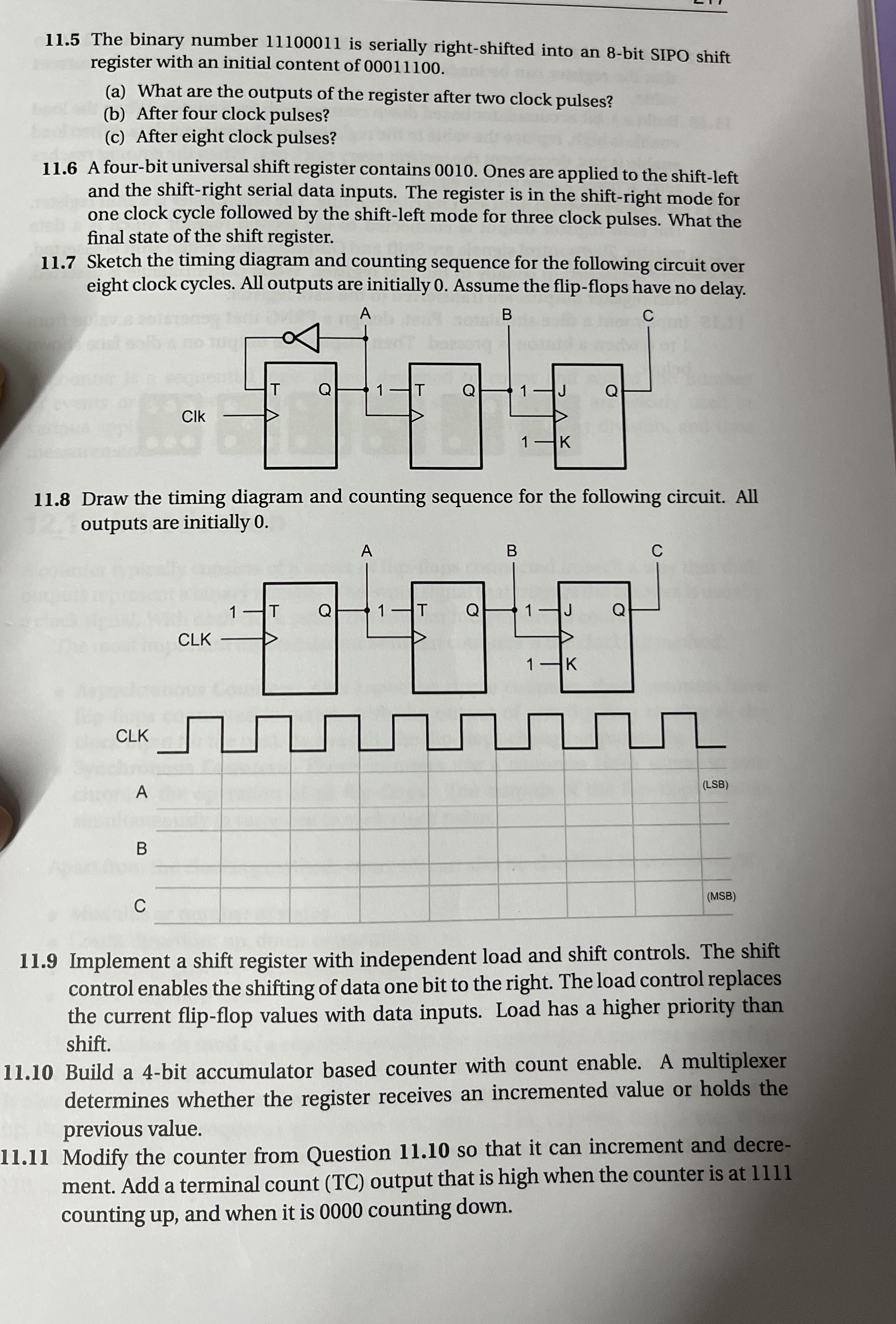

11.5 The binary number 11100011 is serially right-shifted into an 8 -bit SIPO shift register with an initial content of 00011100. (a) What are the outputs of the register after two clock pulses? (b) After four clock pulses? (c) After eight clock pulses? 11.6 A four-bit universal shift register contains 0010 . Ones are applied to the shift-left and the shift-right serial data inputs. The register is in the shift-right mode for one clock cycle followed by the shift-left mode for three clock pulses. What the final state of the shift register. 11.7 Sketch the timing diagram and counting sequence for the following circuit over eight clock cycles. All outputs are initially 0 . Assume the flip-flops have no delay. 11.8 Draw the timing diagram and counting sequence for the following circuit. All outputs are initially 0 . 11.9 Implement a shift register with independent load and shift controls. The shift control enables the shifting of data one bit to the right. The load control replaces the current flip-flop values with data inputs. Load has a higher priority than shift. 11.10 Build a 4-bit accumulator based counter with count enable. A multiplexer determines whether the register receives an incremented value or holds the previous value. 11.11 Modify the counter from Question 11.10 so that it can increment and decrement. Add a terminal count (TC) output that is high when the counter is at 1111 counting up, and when it is 0000 counting down.